HBM

| ||||||||

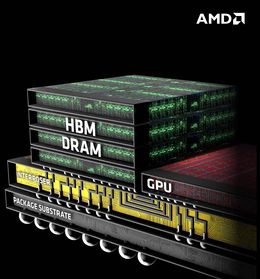

Memorias de alto ancho de banda HBM. AMD reveló detalles sobre su memoria de ancho de banda alta (HBM high bandwidth memory) de interfaz para GPU, comenzando con productos de nueva generación Radeon de la serie 300 de la compañía y, finalmente, APU que combina el procesamiento central de procesador y los gráficos.

Ventajas

El Director de tecnología de AMD Joe Macri dijo que la tecnología era de siete años de desarrollo en la fabricación, . La gran ventaja para el chip fabricante de su rival Nvidia es “al menos un año de retraso” en la high bandwidth memory, por lo que habrá una gran diferencia en el momento que este producto esté en el mercado.

Novedades

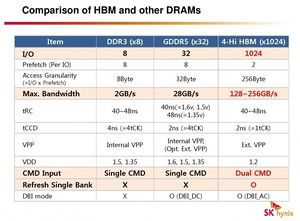

La tecnología consiste en “apilamiento” de chips de RAM para proporcionar hasta tres veces el rendimiento de la memoria GDDR5 dispuestos y utilizados por solo por la GPU. AMD también puede exprimir mucho más las HBM en el espacio ocupado por GDDR5 de memoria convencional, como ejemplo, 1 GB de HBM encaja en una celda de 5 mm por 7 mm, mientras que en las memorias convencionales había necesidad de una huella de 24 mm por 28 mm para 1 GB de GDDR5.

La nueva tecnología de memoria de AMD debe demostrar ser una ventaja casi inmediata para la compañía en el mercado de consumo con este tipo de adelantos en tecnología. AMD ha trabajado durante años para hacer las HBM en una realidad, y creo que tendrán una ventaja en tiempo de lanzamiento al mercado de productos finales con la tecnología, las HBM ayudan a resolver lo que se convertirá en un gran problema en el rendimiento de la memoria de gráficos de escala y poder.

Las Aplicacion en tarjetas gráficas, PC APUs, e incluso algunas cargas de trabajo empresariales. El software para las cargas de trabajo de los consumidores, pero AMD o sus socios tendrán que trabajar duro para hacer un hueco en el mercado HPC.” La nueva interfaz de memoria requiere una nueva especificación y el desarrollo de un “nuevo tipo de chip de memoria con bajo consumo de energía y un ancho de bus ultra-ancha”, que [[AMD[[ lleva a cabo en colaboración con Hynix y otros socios, según lo que informó Hot Hardware.

Fabricación

Los Chips de DRAM HBM se apilan verticalmente, y a través de vías de silicio’(TSVs) y ‘?bumps» que se utilizan para conectar un chip DRAM al siguiente, y luego a una matriz lógica, y en última instancia a la mediadora. Los TSVs y ?bumps se utilizan además para conectar el SoC/GPU para el intercalador y todo el conjunto está conectado en el mismo sustrato de paquete. El resultado final es un solo paquete en el que la GPU/SoC residen en un solo módulo de high bandwidth memory,