Compuerta de tres estado

| ||||||

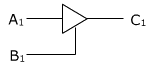

Compuerta de tres estados . Las compuertas de tres estados presentan tres estados de salidas diferentes: un estado de bajo nivel (0), un estado de alto nivel (1), un estado de alta impedancia o estado flotante (Z).

Sumario

Funcionamiento

La compuerta de tres estado funciona normalmente cuando B1 se encuentra en estado alto. Su salida se corresponde con el valor de su entrada. Si B1 se encuentra en estado bajo, su salida cambiará al estado de alta impedancia independientemente del estado en que se encuentre su entrada.

Compuerta inversora de tres estados

La compuerta inversora de tres estado funciona normalmente cuando B2 se encuentra en estado bajo. Su salida se corresponde con el valor de su entrada. Si B2 se encuentra en estado alto, su salida cambiará al estado de alta impedancia independientemente del estado en que se encuentre su entrada.

Compuerta de tres estados TTL

El [circuito] en estado Z se basa en bloquear los dos transistores de la salida Totem-Pole a la vez cuando se active la entrada de control.

En la figura muestra el [inversor] TTL 3-State. La entrada B2 en alto, hace que el transistor T5 se corte; por lo tanto la corriente base colector de T5 satura los transistores T6 y T7.

El diodo D6 conduce y esto produce que los transistores de salida del circuito se corten, debido al potencial bajo en el emisor de T1 y el colector de T2.

La conducción de T1, bloquea a T2 y T4 no recibe corriente en la base, por lo que entra a estado de corte. De otro lado, el colector del transistor T2 queda a un potencial muy próximo a masa, llevando a T3 a corte.

Compuerta de tres estados CMOS

En el circuito CMOS de la figura, el estado de la salida es igual a la entrada sólo si la entrada B1 está en nivel alto (1).

Cuando la entrada B1 está en nivel bajo (0), la salida se encuentra en nivel de impedancia alta (Z) y es independiente del nivel de entrada A1.

En el funcionamiento del circuito interno de la figura, en el estado de entrada B1=0 conduce el transistor QP1 (canal P) y la activación de este elemento hace conducir a QN3 (canal N); por lo tanto el drenador QN3 queda a un potencial de 0 v y esto sitúa al transistor QN5 en estado de corte.

El potencial de 0 v en la puerta del transistor QP3 hace conducir a éste, colocando al transistor QP5 en estado de corte.

En este estado de la entrada de control, los transistores de salida QP5 y QN5 están en corte y el terminal de salida queda en estado de alta impedancia o tercer estado.

Cuando la entrada B1 está en nivel bajo (1), el estado de salida es igual de la entrada, tal como se deduce del funcionamiento del circuito. Si la compuerta tiene estado de entrada A1=1, conduce el transistor QP5 y QN5 entra en corte, lo cual hace la salida C1 igual a 1. Cuando A1=0, conduce el transistor QN5 y QP5 entra en corte, lo cual hace la salida C1 igual a 0.

Fuente

- Artículo:Circuitos lógicos de tres estados. Disponible en “www.solecmexico.com”. Consultado 29 de noviembre de 2011.

- Artículo:Familias Lógicas. Disponible en “www.monografias.com”. Consultado 29 de noviembre de 2011.

- Artículo:Circuitos lógicos. Disponible en “www.slideshare.net”. Consultado 29 de noviembre de 2011.

- Artículo:Simplificación de circuitos lógicos y universalidad de compuertas NAND . Disponible en “www.slideshare.net”. Consultado 29 de noviembre de 2011.