Transistor de efecto campo

| ||||||

El transistor de efecto campo (Field-Effect Transistor o FET, en inglés). Es en realidad una familia de transistores que se basan en el campo eléctrico para controlar la conductividad de un "canal" en un material semiconductor.

Sumario

Tipo de transistores

- FET o JFET (Junction Field Effect Transistor).

- MOST o MOSFET o IGFET (Metal Oxide Semiconductorñ Transistor o Insulated Gate Field Effect Transistor).

Clasificación según el método de aislamiento entre el canal y la puerta

- El MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) usa un aislante (normalmente SiO2).

- El JFET (Junction Field-Effect Transistor) usa una unión p-n

- El MESFET (Metal-Semiconductor Field Effect Transistor) substituye la unión PN del JFET con una barrera Schottky.

- En el HEMT (High Electron Mobility Transistor), también denominado HFET (heterostructure FET), la banda de material dopada con "huecos" forma el aislante entre la puerta y el cuerpo del transistor.

- Los MODFET (Modulation-Doped Field Effect Transistor).

- Los IGBT (Insulated-gate bipolar transistor) es un dispositivo para control de potencia. Son comunmente usados cuando el rango de voltaje drenaje-fuente está entre los 200 a 3000V. Aún así los Power MOSFET todavía son los dispositivos más utilizados en el rango de tensiones drenaje-fuente de 1 a 200V.

- Los FREDFET es un FET especializado diseñado para otorgar una recuperación ultra rápida del transistor.

- Los DNAFET es un tipo especializado de FET que actúa como biosensor, usando una puerta fabricada de moléculas de ADN de una cadena para detectar cadenas de ADN iguales

Simbología

Composición

El transistor de efecto de campo está compuesto por una barra de semiconductor de tipo N (ó P) en la que se difunden dos áreas de semiconductor tipo P (ó N), por lo que el FET tendría cuatro terminales, el drenador, que es uno de los extremos de la barra de semiconductor tipo N, el surtidor, que es el otro extremo del mismo, y dos puertas, que serías las dos áreas de semiconductor tipo P difundias en la barra del semiconductor tipo N. Esto es un FET de doble puerta, aunque normalmente las dos puertas de éste van unidas.

El fet tiene una región N y dos regiones P, por lo que podemos referir las uniones entre estas como diodo puerta-surtidor y diodo puerta-drenador.

Los FETS tienen bastante similitud con los transistores bipolares, por sus terminales.

Terminales

- Bipolar Unipolar

- Emisor E Surtidor S

- Base B Puerta G

- Colector C Drenador D

Ventajas y desventajas del FET

Las ventajas del FET

1. Son dispositivos sensibles a la tensión con alta impedancia de entrada (del orden de 107 W ). Como esta impedancia de entrada es considerablemente mayor que la de los BJT, se prefieren los FET a los BJT para la etapa de entrada de un amplificador multietapa.

2. Los FET generan un nivel de ruido menor que los BJT.

3. Los FET so más estables con la temperatura que los BJT.

4. Los FET son, en general, más fáciles de fabricar que los BJT pues suelen requerir menos pasos de enmascaramiento y difusiones. Es posible fabricar un mayor número de dispositivos en un circuito integrado (es decir, puede obtener una densidad de empaque mayor).

5. Los FET se comportan como resistores variables controlados por tensión para valores pequeños de tensión de drenaje a fuente.

6. La alta impedancia de entrada de los FET les permite almacenar carga el tiempo suficiente para permitir su utilización como elementos de almacenamiento.

7. Los FET de potencia pueden disipar una potencia mayor y conmutar corrientes grandes.

Desventajas del FET

1. Los FET exhiben una respuesta en frecuencia pobre debido a la alta capacitancia de entrada. 2. Algunos tipos de FET presentan una linealidad muy pobre. 3. Los FET se pueden dañar al manejarlos debido a la electricidad estática.

Principio de operación del NJFET

Al igual que sucede con los transistores BJT el JFET tiene tres regiones de operación:

- Región de corte.

- Región lineal.

- Región de saturación

Es preciso hacer notar que en este caso, la saturación alude a un fenómeno completamente distinto al de los transistores BJT.

Región de corte

Centremos nuestra atención en la Figura 1. La zona de tipo P conectada a la puerta forma un diodo con el canal, que es de tipo N. Como se recordará, cuando se forma una unión PN aparecen en los bordes de la misma una zona de deplección en la que no hay portadores de carga libres. La anchura de dicha zona depende de la polarización aplicada. Si esta es inversa, la zona se hace más ancha, proporcionalmente a la tensión aplicada.

Aplicando una tensión VGS negativa aumentamos la anchura de la zona de deplección, con lo que disminuye la anchura del canal N de conducción.

Si el valor de VGS se hace lo suficientemente negativo, la región de agotamiento se extenderá completamente a través del canal, con lo que la resistencia del mismo se hará infinita y se impedirá el paso de ID (Figura 2). El potencial al que sucede este fenómeno se denomina potencial de bloqueo (Pinch Voltage, VP).

Por lo tanto, para valores más negativos que VP el transistor NJFET se encuentra polarizado en la región de corte, y la corriente de drenaje resulta ser nula.

Región lineal

Si en la estructura de la Figura 1 se aplica una tensión VDS mayor que cero, aparecerá una corriente circulando en el sentido del drenaje a la fuente, corriente que llamaremos ID. El valor de dicha corriente estará limitado por la resistencia del canal N de conducción. En este caso pueden distinguirse dos situaciones según sea VDS grande o pequeña en comparación con VGS.

Región de saturación

Si VDS se incrementa más, se llegará a un punto donde el espesor del canal en el extremo del drenaje se acerque a cero. A partir de ese momento, la corriente se mantiene independiente de VDS, puesto que los incrementos de tensión provocan un mayor estrechamiento del canal, con lo que la resistencia global aumenta (Figura 3).

La región de saturación se da cuando se estrangula el canal en el drenaje, lo que sucede cuando la tesión puerta-drenaje es más negativa que VP, es decir:

VGD < VP => VGS - VDS < VP => VDS > VGS - VP

Antes de seguir adelante, comparemos las figuras Figura 2 y Figura En el caso del bloqueo, todo el canal resulta afectado por la zona de deplección, que es constante porque la tensión VGS se aplica uniformemente a lo largo de la unión. En cambio, en la región de corriente constante sólo parte del canal ha llegado al bloqueo (provocado por VDS, que varía a lo largo del mismo), y es lo que permite la circulación de la corriente.

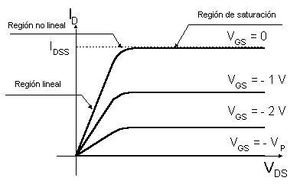

Curvas

Son dos las curvas que se manejan habitualmente para caracterizar los transistores JFET. En primer lugar, en la representación de ID frente a VGS, para una VDS dada, se aprecia claramente el paso de la región de corte a la de saturación (Figura 4).

En la práctica sólo se opera en el segundo cuadrante de la gráfica, puesto que el primero la VGS positiva hace crecer rápidamente IG.

En la característica VDS - ID del transistor NJFET se observa la diferencia entre la regione lineal y de saturación (Figura 5).

En la región lineal, para una determinada VGS, la corriente crece proporcionalmente a la tensión VDS. Sin embargo, este crecimiento se atenúa hasta llegar a ser nulo: se alcanza el valor de saturación, en donde ID sólo depende de VGS.

Nótese que, según esta gráfica, la región de saturación del JFET se identifica con la región activa normal de los transistores bipolares. Mientras que en RAN la corriente de colector sólo depende de la de base, aquí la magnitud de control es la tensión VGS. Por el contrario, si la resistencia del JFET en la región lineal es muy pequeña puede encontrarse un cierto paralelismo entre las regiones lineal de JFET y de saturación del BJT.

Vease también: Electronics Workbench. Simulador de Circutitos Electrónicos

Parametros Comerciales

Se presenta a continuación algunas de las características de los transistores JFET que ofrecen los fabricantes en las hojas de datos:

- IDSS: Es la corriente de drenaje cuando el transistor JFET se encuentra en configuración de fuente común y se cortocircuita la puerta y la fuente (VGS=0). En la práctica marca la máxima intensidad que puede circular por el transistor. Conviene tener en cuenta que los transistores JFET presentan amplias dispersiones en este valor.

- VP (Pinch-Off Voltage): es la tensión de estrangulamiento del canal. Al igual que IDSS, presenta fuertes dispersiones en su valor.

- RDS(ON): Es el inverso de la pendiente de la curva ID/VDS en la zona lineal. Este valor se mantiene constante hasta valores de VGD cercanos a la tensión de estrangulamiento.

- BVDS (Drain-Source Breakdown Voltage): es la tensión de ruptura entre fuente y drenaje. Tensiones más altas que BVDS provocan un fuerte incremento de ID.

- BVGS (Gate-Source Breakdown Voltage): es la tensión de ruptura de la unión entre la puerta y la fuente, que se encuentra polarizada en inversa. Valores mayores de BVGS provocan una conducción por avalancha de la unión.

Enlaces Externos

- Ifet

- Alipso Electronica Transistores

- Electronicafacil

- Monografías

- Transistor de Efecto de Campo

- RincondelVago Transistores de efecto de campo

Fuentes

- Libro Microelectronic de Jacob Millman