Microprocesador 4004

| ||||

Microprocesador 4004. Microprocesador de 4 bits de bus de datos, direcciona 32768 bits de ROM y 5120 bits de RAM. Además se pueden direccionar 16 ports de entrada (de 4 bits) y 16 ports de salida (de 4 bits). Contiene alrededor de 2300 transistores MOS de canal P de 10 micrones. El ciclo de instrucción es de 10,8 microsegundos.

Historia del 4004

En 1969, Silicon Valley, en el estado de California (EE.UU) era el centro de la industria de los semiconductores. Por ello, gente de la empresa Busicom, una joven empresa japonesa, fue a la compañía Intel (fundada el año anterior) para que hicieran un conjunto de doce chips para el corazón de su nueva calculadora de mesa de bajo costo.

Al principio se pensó que no se podía hacer, ya que Intel no estaba preparada para realizar circuitos "a medida". Pero Marcian Edward Ted Hoff, Jr., jefe del departamento de investigación de aplicaciones, pensó que habría una mejor forma de realizar el trabajo.

Durante el otoño (del hemisferio norte) de 1969 Hoff, ayudado por Stanley Mazor, definieron una arquitectura consistente en una CPU de 4 bits, una memoria ROM (de sólo lectura) para almacenar las instrucciones de los programas, una RAM (memoria de lectura y escritura) para almacenar los datos y algunos puertos de entrada/salida para la conexión con el teclado, la impresora, las llaves y las luces. Además definieron y verificaron el conjunto de instrucciones con la ayuda de ingenieros de Busicom (particularmente Masatoshi Shima).

En abril de 1970 Federico Faggin se sumó al staff de Intel. El trabajo de él era terminar el conjunto de chips de la calculadora. Se suponía que Hoff y Mazor habían completado el diseño lógico de los chips y solamente quedaría definir los últimos detalles para poder comenzar la producción. Esto no fue lo que Faggin encontró cuando comenzó a trabajar en Intel ni lo que Shima encontró cuando llegó desde Japón.

Shima esperaba revisar la lógica de diseño, confirmando que Busicom podría realizar su calculadora y regresar a Japón. Se puso furioso cuando vio que estaba todo igual que cuando había ido seis meses antes, con lo que dijo (en lo poco que sabía de inglés) "Vengo acá a revisar. No hay nada para revisar. Esto es sólo idea". No se cumplieron los plazos establecidos en el contrato entre Intel y Busicom. De esta manera, Faggin tuvo que trabajar largos meses, de 12 a 16 horas por día. Finalmente pudo realizar los cuatro chips arriba mencionados. El los llamó "familia 4000". Estaba compuesto por cuatro dispositivos de 16 pines: el 4001 era una ROM de dos kilobits con salida de cuatro bits de datos; el 4002 era una RAM de 320 bits con el port de entrada/salida (bus de datos) de cuatro bits; el 4003 era un registro de desplazamiento de 10 bits con entrada serie y salida paralelo; y el 4004 era la CPU de 4 bits.

El 4001 fue el primer chip diseñado y terminado. La primera fabricación ocurrió en octubre de 1970 y el circuito trabajó perfectamente. En noviembre salieron el 4002 con un pequeño error y el 4003 que funcionó correctamente. Finalmente el 4004 vino unos pocos días antes del final de 1970. Fue una lástima porque en la fabricación se habían olvidado de poner una de las máscaras. Tres semanas después vinieron los nuevos 4004, con lo que Faggin pudo realizar las verificaciones. Sólo encontró unos pequeños errores.

En febrero de 1971 el 4004 funcionaba correctamente. En el mismo mes recibió de Busicom las instrucciones que debían ir en la ROM. A mediados de marzo de 1971, envió los chips a Busicom, donde verificaron que la calculadora funcionaba perfectamente. Cada calculadora necesitaba un 4004, dos 4002, cuatro 4001 y tres 4003. Tomó un poco menos de un año desde la idea al producto funcionando correctamente. Luego de que el primer microprocesador fuera una realidad, Faggin le pidió a la gerencia de Intel que utilizara este conjunto de chips para otras aplicaciones. Esto no fue aprobado, pensando que la familia 4000 sólo serviría para calculadoras. Además, como fue producido mediante un contrato exclusivo, sólo lo podrían poner en el mercado teniendo a Busicom como intermediario. Después de hacer otros dispositivos utilizando la familia 4000, Faggin le demostró a Robert Noyce (entonces presidente de Intel) la viabilidad de estos integrados para uso general. Finalmente ambas empresas llegaron a un arreglo: Intel le devolvió los 60000 dólares que había costado el proyecto, sólo podría vender los integrados para aplicaciones que no fueran calculadoras y Busicom los obtendría más baratos (ya que se producirían en mayor cantidad).

El 15 de noviembre de 1971, la familia 4000, luego conocida como MCS-4 (Micro Computer System 4-bit) fue finalmente introducida en el mercado.

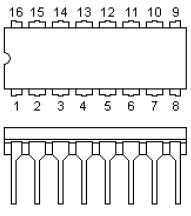

Terminales del 4004

Este microprocesador estaba encapsulado en el formato DIP (Dual Inline Package) de 16 patas (ocho de cada lado). La distancia entre las patas es de 0,1 pulgadas (2,54 milímetros), mientras que la distancia entre patas enfrentadas es de 0,3 pulgadas (7,68 milímetros). Nótese en la primera imágen que identifica la posición de la pata 1. Esto sirve para no insertar el chip al revés en el circuito impreso.

Funciones

Las funciones de las 16 patas con las que se conecta el 4004 con el exterior son las siguientes:

| Pata | Nombre | Descripción |

|---|---|---|

| 1 | D0 | Todas las direcciones y datos de RAM y ROM pasan por estas líneas |

| 2 | D1 | Todas las direcciones y datos de RAM y ROM pasan por estas líneas |

| 3 | D2 | Todas las direcciones y datos de RAM y ROM pasan por estas líneas |

| 4 | D3 | Todas las direcciones y datos de RAM y ROM pasan por estas líneas |

| 5 | Vss | Referencia de tierra. Es la tensión más positiva. |

| 6 | Clock phase 1 | Una de las dos fases de entrada de reloj (clock) |

| 7 | Clock phase 2 | La otra de las dos fases de entrada de reloj (clock) |

| 8 | Sync output | Señal de sincronismo generada por el procesador. Indica el comienzo de un ciclo de instrucción. |

| 9 | Reset | Un "1" lógico aplicado en esta pata borra todos los flags y registros de estado y fuerza el contador de programa (PC) a cero. Para que actúe correctamente, esta línea deberá activarse por 64 ciclos de reloj (8 ciclos de máquina). |

| 10 | Test | La instrucción JCN verifica el estado de esta línea. |

| 11 | CM-ROM (Control Memory Outputs) | Esta señal está activa cuando el procesador necesita datos de la

ROM |

| 12 | VDD | Alimentación del microprocesador. La tensión debe ser de -15V +/- 5% |

| 13 | CM-RAM3 | Éstas son las señales de selección de banco para indicar a cuál RAM 4002 desea acceder el microprocesador |

| 14 | CM-RAM2 | Éstas son las señales de selección de banco para indicar a cuál

RAM 4002 desea acceder el microprocesador |

| 15 | CM-RAM1 | Éstas son las señales de selección de banco para indicar a cuál

RAM 4002 desea acceder el microprocesador |

| 16 | CM-RAM0 | Éstas son las señales de selección de banco para indicar a cuál

RAM 4002 desea acceder el microprocesador |

Instrucciones del 4004

Hay instrucciones de uno o dos bytes. Los primeros tardan 8 períodos de reloj (un ciclo de instrucción). Los segundos tardan 16 períodos de reloj (dos ciclos de instrucción). Entre otras, éstas son las instrucciones más significtivas:

| Mnemotécnico | Descripción |

|---|---|

| NOP | No hace nada |

| JCN | Salta a la dirección especificada por A2 A2 A2 A2 A1 A1 A1 A1 dentro de la misma ROM que contiene esta instrucción JCN, si se cumple la condición C1 C2 C3 C4, en caso contrario continúa ejecutando la próxima instrucción.

|

| FIM | Cargar el dato D2, D1 (ocho bits) en el par de registros RRR |

| SRC | Enviar la dirección (contenido del par de registros RRR) a la ROM y a la RAM en los tiempos X2 y X3 del ciclo de instrucción |

| FIN | Cargar en el par de registros RRR el dato de ROM apuntado por el par de registros cero |

| JIN | Salto indirecto según el par de registros RRR |

| JUN | Salto incondicional a la dirección de ROM A3, A2, A1 |

| JMS | Salvar el viejo valor del contador de programa y saltar

a la dirección de ROM A3, A2, A1 |

| INC | Incrementar el contenido del registro RRRR |

| ISZ | Incrementar el registro RRRR. Si el resultado no es cero, saltar a la dirección A2 A2 A2 A2 A1 A1 A1 A1 dentro de la misma ROM que contiene esta instrucción ISZ |

| ADD | Sumar el registro RRRR al acumulador con acarreo |

| SUB | Restar el registro RRRR del acumulador con préstamo |

| LD | Cargar el acumulador con el contenido del registro RRRR |

| XCH | Intercambiar los contenidos del acumulador y el registro RRRR |

| BBL | Retornar de subrutina y cargar el dato D D D D en el acumulador |

| LDM | Cargar el dato D D D D en el acumulador |

Fuentes

- Microprossesor Intel, pp. 187-196.

- Los microprocesadores Intel.