Front-side bus

| ||||||||

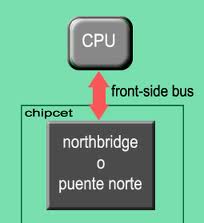

Front-side bus, también conocido por su acrónimo FSB (del inglés literalmente "bus de la parte frontal"), y se refiere a la interfaz de comunicación externa del procesador con el chipset y el resto del sistema informático, a diferencia de back-side bus (literalmente bus trasero o bus de la parte de atrás) que conecta la memoria caché (y potencialmente otros CPUs) El FSB incluye señales de datos, direcciones y control, así como señales de reloj que sincronizan su funcionamiento.

Historia

El término comenzó a usarse por Intel Corporation en la década de 1990, con la salida de los microprocesadores Pentium Pro y Pentium II. Este diseño representó una mejora del rendimiento con respecto al bus de sistema de las décadas anteriores y empezó a formar parte de la arquitectura de computadoras estándar desde que las aplicaciones requirieron más memoria de la que el procesador podría retener.

En los diseños mas actuales el FSB se utilizó a modo de conexión exclusiva principal entre el microprocesador y el circuito integrado auxiliar o chipset, (generalmente compuesto por el puente norte o northbridge y el puente sur o southbridge) que es el encargado de interconectar el resto de buses del sistema. Los buses como PCI, PCI Express, y buses de memoria se comunican con el chipset para permitir el correcto flujo de datos entre los diferentes dispositivos. Generalmente estos buses secundarios funcionan a una velocidad derivada de la velocidad del FSB.

Pese a la solución que dio al problema, empresas como AMD siempre han criticado el FSB, ya que limita las capacidades reales de un sistema generando mucha latencia y un tiempo de respuesta mayor, creando un auténtico cuello de botella para el resto de dispositivos.

No fue hasta 2001 y la aparición de la tecnología HyperTransport empleada por AMD, que se pudo reemplazar el uso del FSB. Actualmente empresas fabricantes de chipsets como NVIDIA, Silicon Integrated Systems o VIA Technologies, ya han comenzado a eliminar el uso del FSB sustituyéndolo con la versión 3.0 de HyperTransport. En los nuevos procesadores de Intel, desde Nehalem, se emplea otro tipo de bus como el Intel QuickPath Interconnect.

Velocidad y Ancho de Banda

La frecuencia de trabajo del microprocesador se obtiene como resultado de multiplicar la frecuencia de reloj del FSB (en megahercios, no en MT/s) por un factor multiplicador. Este factor multiplicador, así como la frecuencia de reloj del FSB pueden alterarse a través de la configuración de la placa base, generalmente a través de la BIOS, permitiendo así el overclocking. Por ejemplo, una CPU de 1.000 MHz podría funcionar con una frecuencia de reloj de 133 MHz y un factor multiplicador de 7,5.

El ancho de banda del FSB depende de su tamaño de palabra (si es de 16, 32 o 64 bits), su frecuencia de reloj medida en megahercios y el número de transferencias que realiza por cíclo de reloj. Por ejemplo, un FSB de 32 bits de ancho (4 bytes), funcionando a 100 MHz y que realice 4 transferencias por cada ciclo, ofrece un máximo teórico de 1.600 megabytes por segundo.

4 bytes x 100 MHz x 4 transferencias/ciclo = 1.600 MB/s. Por otra parte si se usa la tecnología Quad Pumping, si el bus funciona a 100 MHz de señal de reloj, en cada ciclo de reloj hay cuatro transferencias de datos. Se dice entonces que el bus funciona a 400 MT/s.

Véase también

- Back-side bus

- HyperTransport

- Intel QuickPath Interconnect