Diferencia entre revisiones de «Sumador completo»

m (Texto reemplazado: «<div align="justify">» por «») |

|||

| (No se muestran 4 ediciones intermedias de 2 usuarios) | |||

| Línea 1: | Línea 1: | ||

| − | |||

{{Definición | {{Definición | ||

| − | |||

|nombre=Sumador completo | |nombre=Sumador completo | ||

| − | + | |imagen=Sumacom.jpg | |

| − | |imagen= | ||

| − | |||

|tamaño= | |tamaño= | ||

| − | + | |concepto=Es un circuito combinacional que realiza la suma de dos bit y un acarreo de entrada, obteniendo en su salida la suma y un acarreo de salida. | |

| − | |concepto=Es un circuito combinacional que realiza la suma de dos bit y un | + | }} |

| − | obteniendo en su salida la suma y un acarreo de salida. | + | '''Sumador completo'''. En este ejemplo las entradas son A,B y C<sub>in</sub>. A y B son los [[bits]] de entrada, C<sub>in</sub> el acarreo de entrada. La salida es S, y C<sub>out</sub> la salida de acarreo. Está compuesto por dos compuertas OR - Exclusiva, tres compuertas AND y una OR de tres entradas. |

| − | |||

| − | }} | ||

| − | |||

| − | '''Sumador completo'''. En este ejemplo las entradas son A,B y | ||

| − | |||

| − | |||

| Línea 24: | Línea 14: | ||

En la siguiente tabla de la verdad muestra los resultado de este [[circuito]]. | En la siguiente tabla de la verdad muestra los resultado de este [[circuito]]. | ||

| − | [[Imagen: | + | [[Imagen:Tablacom.jpg|thumb|200px|center]] |

==Salida S== | ==Salida S== | ||

| Línea 30: | Línea 20: | ||

Esta salida corresponde a la operación de la compuerta lógica [[OR- Exclusiva]]: | Esta salida corresponde a la operación de la compuerta lógica [[OR- Exclusiva]]: | ||

| − | S = A·B’·Cin’ + A’·B·Cin’ + A·B·Cin + A’·B’·Cin | + | * S = A·B’·Cin’ + A’·B·Cin’ + A·B·Cin + A’·B’·Cin |

| − | + | * S = Cin’·(A·B’ + A’·B) + Cin ·(A·B + A’·B’) | |

| − | S = Cin’·(A·B’ + A’·B) + Cin ·(A·B + A’·B’) | + | * S = Cin’·(A·B’ + A’·B) + Cin ·(A’·A + A’·B’ + A·B + B·B’) |

| − | + | * S = Cin’·(A·B’ + A’·B) + Cin ·((A’ + B)·(A + B’)) | |

| − | S = Cin’·(A·B’ + A’·B) + Cin ·(A’·A + A’·B’ + A·B + B·B’) | + | * S = Cin’·(A·B’ + A’·B) + Cin ·((A·B’)’·(A’·B)’) |

| − | + | * S = Cin’·(A·B’ + A’·B) + Cin ·(A·B’ + A’·B)’ | |

| − | S = Cin’·(A·B’ + A’·B) + Cin ·((A’ + B)·(A + B’)) | + | * S = (A Å B) Å Cin |

| − | |||

| − | S = Cin’·(A·B’ + A’·B) + Cin ·((A·B’)’·(A’·B)’) | ||

| − | |||

| − | S = Cin’·(A·B’ + A’·B) + Cin ·(A·B’ + A’·B)’ | ||

| − | |||

| − | S = (A Å B) Å Cin | ||

==Salida Cout== | ==Salida Cout== | ||

| Línea 57: | Línea 41: | ||

==Circuito lógico== | ==Circuito lógico== | ||

| − | [[Imagen: | + | [[Imagen:Sumacom.jpg|thumb|200px|center]] |

==Aplicación== | ==Aplicación== | ||

En las computadoras se encuentran en la [[Unidad Aritmético Lógica]], realizan la operación en [[código binario]] decimal o [[BCD]] exceso 3, generalmente usan el código binario. | En las computadoras se encuentran en la [[Unidad Aritmético Lógica]], realizan la operación en [[código binario]] decimal o [[BCD]] exceso 3, generalmente usan el código binario. | ||

| − | |||

| − | |||

== Fuentes == | == Fuentes == | ||

*Artículo: [http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030901.htm Universidad de Colombia]. Disponible en; “www.virtual.unal.edu.co”. Consultado: 8 de febrero de 2012. | *Artículo: [http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/030901.htm Universidad de Colombia]. Disponible en; “www.virtual.unal.edu.co”. Consultado: 8 de febrero de 2012. | ||

| − | |||

*Artículo: [http://es.wikipedia.org/wiki/Sumador wikipedia]. Disponible en; “wikipedia.org”. Consultado: 8 de febrero de 2012. | *Artículo: [http://es.wikipedia.org/wiki/Sumador wikipedia]. Disponible en; “wikipedia.org”. Consultado: 8 de febrero de 2012. | ||

| − | |||

| − | |||

[[Category:Electrónica_digital]] | [[Category:Electrónica_digital]] | ||

última versión al 19:13 3 sep 2019

| ||||||

Sumador completo. En este ejemplo las entradas son A,B y Cin. A y B son los bits de entrada, Cin el acarreo de entrada. La salida es S, y Cout la salida de acarreo. Está compuesto por dos compuertas OR - Exclusiva, tres compuertas AND y una OR de tres entradas.

Tabla de la verdad

En la siguiente tabla de la verdad muestra los resultado de este circuito.

Salida S

Esta salida corresponde a la operación de la compuerta lógica OR- Exclusiva:

- S = A·B’·Cin’ + A’·B·Cin’ + A·B·Cin + A’·B’·Cin

- S = Cin’·(A·B’ + A’·B) + Cin ·(A·B + A’·B’)

- S = Cin’·(A·B’ + A’·B) + Cin ·(A’·A + A’·B’ + A·B + B·B’)

- S = Cin’·(A·B’ + A’·B) + Cin ·((A’ + B)·(A + B’))

- S = Cin’·(A·B’ + A’·B) + Cin ·((A·B’)’·(A’·B)’)

- S = Cin’·(A·B’ + A’·B) + Cin ·(A·B’ + A’·B)’

- S = (A Å B) Å Cin

Salida Cout

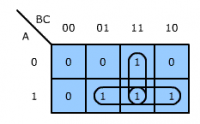

La salida Cout está dada por:

Cout = A·B + A·Cin + B·Cin

El mapa de karnaugh de la salida Cout se muestra en la siguiente figura.

Circuito lógico

Aplicación

En las computadoras se encuentran en la Unidad Aritmético Lógica, realizan la operación en código binario decimal o BCD exceso 3, generalmente usan el código binario.

Fuentes

- Artículo: Universidad de Colombia. Disponible en; “www.virtual.unal.edu.co”. Consultado: 8 de febrero de 2012.

- Artículo: wikipedia. Disponible en; “wikipedia.org”. Consultado: 8 de febrero de 2012.