Biestable

| ||||

Biestable. Circuito secuencial en que su salida no sólo depende de su entrada, sino de sus entradas anteriores, que quedan recogidas en lo que se conoce como estado.

Sumario

Clasificación

Los circuitos lógicos se clasifican en dos tipos:

- Combinacionales: aquellos cuyas salidas sólo dependen de las entradas actuales.

- Secuenciales: aquellos cuyas salidas dependen no sólo de sus entradas actuales, sino también de sus entradas anteriores. Esta “información” de las entradas anteriores, debe preservarse en el circuito y se denomina estado interno, secundario, o simplemente estado, del circuito. Es necesario distinguir el valor presente de una señal del que poseía en un instante inmediatamente anterior, y éste del anterior. Por ello habrá una intervención explícita del tiempo.

La base de los circuitos secuenciales es el biestable, es el dispositivo más pequeño que es capaz de memorizar la información a la que antes se hacía referencia. Almacena el estado 0 ó el estado 1, y por ello recibe el nombre de biestable, tienen dos estados estables de funcionamiento. También se les suele conocer como FLIP-FLOPS.

Biestables

Los biestables pueden ser:

- Asíncronos: Los cambios se producen en cualquier momento en que cambien las entradas. (RS y JK).

- Síncronos: Los cambios se producen en el momento en que lo ordene un reloj.

Síncronos

A su vez los biestables síncronos pueden ser:

- Disparados por nivel: Los cambios son efectivos cuando la entrada de disparo del biestable está a un nivel activo, durante todo el tiempo que dura el dicho nivel. (RS, JK y D).

- Disparados por flanco: Los cambios se producen sólo en los momentos de cambios del reloj (flancos, transiciones). (RS, JK, D y T).

- Maestro / Esclavo (Master / Slave): (RS, JK, D y T).

Biestable RS

Tiene dos entradas S(set) y R(reset), y tiene dos salidas complementarias Q (qn) y Q, tiene además una entrada CLK(reloj) que viene a ser una entrada de habilitación: Biestable RS (Set Reset) síncrono.

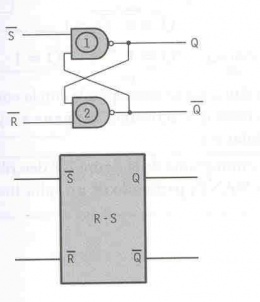

Además de las entradas R y S, posee una entrada C de sincronismo cuya misión es la de permitir o no el cambio de estado del biestable. En la siguiente figura se muestra un ejemplo de un biestable síncrono a partir de una asíncrona, junto con su esquema normalizado: Tabla de verdad

| C | R | S | Q(NOR) |

|---|---|---|---|

| 0 | x | x | q |

| 1 | 0 | 0 | q |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | N.D. |

N.D = Estado no deseado, q= Estado de memoria

Biestable RS (Set Reset) asíncrono: Sólo posee las entradas R y S. Se compone internamente de dos puertas lógicas NAND o NOR, según se muestra en la siguiente figura: Tabla de verdad

| R | S | Q (NOR) | Q'(NAND) |

|---|---|---|---|

| 0 | 0 | q | N.D. |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | N.D. | q |

Biestable JK asíncrono

El biestable JK puede considerarse como el biestable universal. Dispone de tres entradas síncronas J y K, para especificar la operación y CLK, para disparar el biestable. También consta de dos entradas asíncronas PR y CLR, y por supuesto dos salidas complementarias.

Tabla de verdad:

| C | R | S | Q(NOR) |

|---|---|---|---|

| 0 | x | x | q |

| 1 | 0 | 0 | q |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | N.D. |

X = no importa

Biestable T

Se trata de un biestable que cambia de estado con cada pulso de reloj:

| J | K | Q | Qsiguiente |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | x | 0 |

| 1 | 0 | x | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

X = no importa

Biestable D (Latch)

Se trata de otro tipo de Biestable, esta vez, con una entrada D(datos) y dos salidas de estados complementarias, Q. Cuenta además con una entrada de CLK(reloj), que funciona como habilitador “disparando” el biestable. También puede contar con dos entradas más, conocidas por PR (de preset: reiniciar) y CLR (de clear: despejar). El Biestable D puede funcionar de dos formas:

- Síncrona: Usa una señal de reloj.

- Asíncrona: Usa las señales PR Y CLR.

De forma síncrona lo hace de la siguiente manera: Si la transición de la señal de reloj es de bajo a alto (o sea, de 0 a 1) se traslada el dato D a la salida, se dice que el biestable ha sido disparado por la señal de reloj. Si por el contrario la transición en el pulso de reloj es de estado alto a bajo (o sea, pasa de 1 a 0) el biastable no responde.

Las entradas PR y CLR son lo que se llaman entradas asíncronas, pues independientemente de cómo esté la señal de reloj, reiniciarán (pondrán un 1 en la salida) o despejarán (pondrán un 0 en la salida) el biestable. Éste es el modo de funcionamiento asíncrono. Tabla de verdad {| class="wikitable" border="1" |- ! D ! Q ! Qsiguiente |- | 0 | x | 0 |- | 1 | x | 1 |} X = no importa

Biestable Master & Slave (Maestro-Esclavo)

La mayor parte de los sistemas digitales complejos operan con un sistema secuencial síncrono, lo que requiere un reloj maestro que envíe señales a todas las partes del sistema para coordinar la operación del mismo.

Los biestables vistos transfieren la entrada a la salida cuando se lo indica el cambio en la señal de reloj. Ya se ha visto que están disparados por flancos de subida o de bajada. Pero muchos biestables son dispositivos disparados por pulsos, denominándose biestables maestro-esclavo. Un biestable maestro-esclavo está formado por varias puertas y flips-flops conectados de manera que se usa el pulso completo de reloj (tiempo que el reloj está a nivel alto) para transmitir el dato de la entrada a la salida.

Aplicaciones

Un biestable puede usarse para almacenar un bit. La información contenida en muchos biestables puede representar el estado de un secuenciador, el valor de un contador, un carácter ASCII en la memoria de un ordenador, o cualquier otra clase de información. Un uso corriente es el diseño de máquinas de estado finitas electrónicas. Los biestables almacenan el estado previo de la máquina que se usa para calcular el siguiente.

El T es útil para contar. Una señal repetitiva en la entrada de reloj hace que el biestable cambie de estado por cada transición alto-bajo si su entrada T está a nivel 1. La salida de un biestable puede conectarse a la entrada de reloj de la siguiente y así sucesivamente. La salida final del conjunto considerado como una cadena de salidas de todos los biestables es el conteo en código binario del número de ciclos en la primera entrada de reloj hasta un máximo de 2n-1, donde n es el número de biestables usados.

Uno de los problemas con esta configuración de contador (ripple counter en inglés) es que la salida es momentáneamente inválida mientras los cambios se propagan por la cadena justo después de un flanco de reloj. Hay dos soluciones a este problema. La primera es muestrear la salida sólo cuando se sabe que esta es válida. La segunda, más compleja y ampliamente usada, es utilizar un tipo diferente de contador síncrono, que tiene una lógica más compleja para asegurar que todas las salidas cambian en el mismo momento predeterminado, aunque el precio a pagar es la reducción de la frecuencia máxima a la que puede funcionar.

Una cadena de biestables T como la descrita anteriormente también sirve para la división de la frecuencia de entrada entre 2n, donde n es el número de biestables entre la entrada y la última salida.