Diferencia entre revisiones de «Familia Lógica ECL»

(Página creada con '{{Objeto|nombre= Familia Lógica ECL|imagen= Porecl.JPG|descripcion= Lógica ECL}} <div align="justify"> ''' Familia Lógica ECL''' La familia ECL, lo que quiere decir Lógi...') (Etiqueta: no tiene enlaces internos) |

|||

| Línea 1: | Línea 1: | ||

| − | {{Objeto|nombre= Familia Lógica ECL|imagen= Porecl.JPG|descripcion= Lógica ECL}} | + | {{Objeto|nombre= Familia Lógica ECL|imagen= Porecl.JPG|descripcion= Lógica ECL}} |

| + | |||

<div align="justify"> | <div align="justify"> | ||

''' Familia Lógica ECL''' | ''' Familia Lógica ECL''' | ||

| − | La familia ECL, lo que quiere decir Lógica Acoplada en Emisor (emmiter-coupled logic) son unos circuitos integrados digitales los cuales usan transistores bipolares, pero a diferencia de los TTL en los ECL se evita la saturación de los transistores, esto da lugar a un incremento en la velocidad total de conmutación. La familia ECL opera bajo el principio de la conmutación de corriente, por el cual una corriente de polarización fija menor que la corriente del colector de saturación es conmutada del colector de un transistor al otro. Este tipo de configuraciones se les conoce también como la lógica de modo de corriente (CML; current-mode logic). | + | La familia ECL, lo que quiere decir Lógica Acoplada en Emisor (emmiter-coupled logic) son unos circuitos integrados digitales los cuales usan transistores bipolares, pero a diferencia de los TTL en los ECL se evita la saturación de los transistores, esto da lugar a un incremento en la velocidad total de conmutación. La [[familia]] ECL opera bajo el principio de la conmutación de corriente, por el cual una corriente de polarización fija menor que la corriente del colector de saturación es conmutada del colector de un [[transistor]] al otro. Este tipo de configuraciones se les conoce también como la lógica de modo de corriente (CML; current-mode logic). |

== Fundamento de las ECL == | == Fundamento de las ECL == | ||

| − | El funcionamiento de los circuitos ECL se basa en el mismo | + | El funcionamiento de los circuitos ECL se basa en el mismo delamplificador [[diferencial]]. Los transistores no se saturan, la operación normal es en zona activa, lo que constituye una de las razones que hace que estos circuitos sean los mas veloces de los circuitos integrados digitales. |

== La configuración de una ECL == | == La configuración de una ECL == | ||

| Línea 13: | Línea 14: | ||

| − | [[Image:ECL.JPG|thumb| | + | [[Image:ECL.JPG|thumb|left|367x309px|Lógica de emisor acoplado o ECL]] |

| + | |||

| + | |||

| + | |||

| + | |||

| Línea 37: | Línea 42: | ||

Puesto que en el amplificador diferencial ningún transistor está dispuesto a llegar a saturación, se elimina el tiempo de almacenamiento y, por tanto, la lógica ECL se convierte en la más rápida de las familias lógicas. Podemos conseguir retardos de propagación inferiores a 0,5 nanosegundos por puerta. | Puesto que en el amplificador diferencial ningún transistor está dispuesto a llegar a saturación, se elimina el tiempo de almacenamiento y, por tanto, la lógica ECL se convierte en la más rápida de las familias lógicas. Podemos conseguir retardos de propagación inferiores a 0,5 nanosegundos por puerta. | ||

| + | |||

| + | |||

| + | === Lógica cableada con circuitos ECL === | ||

| + | |||

| + | Al igual que en las otras familias resulta conveniente obtener un nivel adicional de [[lógica]] a través de la unión de varias salidas de compuertas ECL. Cuando dos o mas salidas de estas compuertas se unen, en el punto de las mismas se realiza la función OR de las salidas unidas. | ||

| Línea 42: | Línea 52: | ||

1- Son los circuitos más veloces y pueden alcanzar tiempos de demora de hasta 1ns. | 1- Son los circuitos más veloces y pueden alcanzar tiempos de demora de hasta 1ns. | ||

| − | 2- No existen picos de corrientes en los transistores como sucede en la familia | + | |

| + | 2- No existen picos de corrientes en los transistores como sucede en la familia lógica | ||

| + | TTL. | ||

| + | |||

3- Se dispone de salidas complementadas, lo que le brinda mayor versatilidad. | 3- Se dispone de salidas complementadas, lo que le brinda mayor versatilidad. | ||

| + | |||

4- El nivel de 1 lógica es prácticamente independiente del factor de carga. | 4- El nivel de 1 lógica es prácticamente independiente del factor de carga. | ||

| + | |||

5- Buen factor de carga N= 15 | 5- Buen factor de carga N= 15 | ||

| Línea 51: | Línea 66: | ||

1- Pequeños valores de los márgenes de ruidos. | 1- Pequeños valores de los márgenes de ruidos. | ||

| + | |||

2- Altos valores de potencia del orden de 40 mW. | 2- Altos valores de potencia del orden de 40 mW. | ||

| + | |||

3- No son compatibles con los circuitos TTL. | 3- No son compatibles con los circuitos TTL. | ||

| + | |||

4- Ocupan gran área en los circuitos integrados | 4- Ocupan gran área en los circuitos integrados | ||

| − | |||

| − | |||

| − | |||

| − | |||

== Aplicación de las ECL == | == Aplicación de las ECL == | ||

| Línea 65: | Línea 79: | ||

=== Ejemplo === | === Ejemplo === | ||

| + | |||

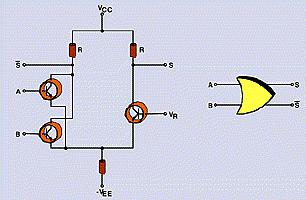

| + | Puerta OR/NOR de dos entradas y su representación esquemática, en una familia ECL | ||

| + | |||

| + | [[Image:Nor.JPG|thumb|left|367x309px|Puerta OR/NOR a ECL]] | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| − | |||

| − | |||

</div> | </div> | ||

Revisión del 17:48 22 oct 2011

| ||||

Familia Lógica ECL La familia ECL, lo que quiere decir Lógica Acoplada en Emisor (emmiter-coupled logic) son unos circuitos integrados digitales los cuales usan transistores bipolares, pero a diferencia de los TTL en los ECL se evita la saturación de los transistores, esto da lugar a un incremento en la velocidad total de conmutación. La familia ECL opera bajo el principio de la conmutación de corriente, por el cual una corriente de polarización fija menor que la corriente del colector de saturación es conmutada del colector de un transistor al otro. Este tipo de configuraciones se les conoce también como la lógica de modo de corriente (CML; current-mode logic).

Sumario

Fundamento de las ECL

El funcionamiento de los circuitos ECL se basa en el mismo delamplificador diferencial. Los transistores no se saturan, la operación normal es en zona activa, lo que constituye una de las razones que hace que estos circuitos sean los mas veloces de los circuitos integrados digitales.

La configuración de una ECL

Está basada en el amplificador diferencial, denominado así porque su salida es proporcional a la diferencia entre dos tensiones de entrada V1 y V2. Este circuito se utiliza principalmente en sistemas analógicos, pero también tiene propiedades digitales, llegando a ser la base de construcción de la lógica de emisor acoplado o ECL (en algunos casos nos la podemos encontrar como lógica de modo corriente o CML), como lo muestra el circuito.

Al aumentar el número de entradas, es necesario poner dos seguidores de emisor para igualar niveles de tensión de entrada y salida

Si V1 es igual que V2 tendremos que, por simetría del circuito, las corrientes de los transistores son iguales. Sin embargo, si V1 sobrepasa a V2 en aproximadamente 0,1 voltio, el transistor T1 estará en conducción y T2 en corte; e inversamente, si V1 es menor que V2 en 0,1 voltio, entonces T2 conducirá y T1 estará en corte.

La corriente de emisor se mantiene prácticamente constante, y se transfiere o conmuta del transistor T1 al T2 cuando la tensión V1 varía desde 0,1 V, por encima de la tensión de referencia V2, hasta 0,1 voltios por debajo de esta tensión. Excepto dentro de un margen muy estrecho de variación de la tensión de entrada V1, a la salida S sólo puede tener uno de dos posibles valores y, por tanto, actúa como circuito digital. Los dos niveles lógicos pueden deducirse fácilmente. Si T2 está en corte, la tensión de salida será igual a la de alimentación y estaremos a nivel lógico 1. Cuando T2 está en conducción, los valores de las resistencias calculados previamente harán que el transistor se encuentre en su zona activa, es decir, T2 estará en su región activa cuando la unión colector-base esté polarizada inversamente. Entonces, la tensión de salida será la de alimentación menos la caída de tensión en la resistencia de colector, obteniendo de esta manera el estado lógico 0.

Puesto que en el amplificador diferencial ningún transistor está dispuesto a llegar a saturación, se elimina el tiempo de almacenamiento y, por tanto, la lógica ECL se convierte en la más rápida de las familias lógicas. Podemos conseguir retardos de propagación inferiores a 0,5 nanosegundos por puerta.

Lógica cableada con circuitos ECL

Al igual que en las otras familias resulta conveniente obtener un nivel adicional de lógica a través de la unión de varias salidas de compuertas ECL. Cuando dos o mas salidas de estas compuertas se unen, en el punto de las mismas se realiza la función OR de las salidas unidas.

Ventajas de la familia ECL

1- Son los circuitos más veloces y pueden alcanzar tiempos de demora de hasta 1ns.

2- No existen picos de corrientes en los transistores como sucede en la familia lógica TTL.

3- Se dispone de salidas complementadas, lo que le brinda mayor versatilidad.

4- El nivel de 1 lógica es prácticamente independiente del factor de carga.

5- Buen factor de carga N= 15

Desventajas de la familia ECL

1- Pequeños valores de los márgenes de ruidos.

2- Altos valores de potencia del orden de 40 mW.

3- No son compatibles con los circuitos TTL.

4- Ocupan gran área en los circuitos integrados

Aplicación de las ECL

En la construcción de diferentes tipos de compuertas que requieren de las características de las ECL.

Ejemplo

Puerta OR/NOR de dos entradas y su representación esquemática, en una familia ECL

Fuente

- Microelectronics, Jacob Millman, 1979

- Electrónica Digital. Julio Díaz Calvo. Editorial Pueblo y Educación, 1989