PDP-8

| ||||

PDP-8 El PDP-8 12 bits fue la primera minicomputadora éxito comercial, producido por Digital Equipment Corporation en la década de 1960. Fue el primer ordenador vendido en la serie DEC PDP de las computadoras. El jefe de ingenieros que diseñó la primera versión del PDP-8 fue Edson de Castro, quien más tarde fundó Data General.

Sumario

- 1 Historia

- 2 Importancia arquitectónica

- 3 Descripción

- 4 Las versiones de la PDP-8

- 5 Entrada/Salida

- 6 Instalaciones de programación

- 7 Conjunto de instrucciones

- 8 Páginas de memoria

- 9 Las instrucciones básicas

- 10 Dispositivo

- 11 Función

- 12 Control de la memoria

- 13 Virtualización

- 14 Lista de enlaces

- 15 Interrupciones

- 16 Fuentes

Historia

El 22 de Marzo de 1965 Digital Equipment Corporation presenta la PDP-8, la primera minicomputadora, que es reconocida como la más importante en la década de 1960. Era la computadora paralela para uso general más económica del mercado costando únicamente US$20,000.00, y también fue la primera computadora vendida al menudeo y la primera computadora digital paralela de uso general vendida en configuración de sobremesa. Esto fue seguido por el PDP-8/S, disponible en los modelos de escritorio y de montaje en rack. Mediante el uso de una aplicación ALU serie de un bit, el PDP-8/S era más pequeño, menos costoso, pero mucho más lento que el original PDP-8 - La única masa periférica de almacenamiento disponible para el PDP-8/S era el disco DF32. En 1975, los primeros ordenadores personales basados en microprocesadores de bajo costo, como el MITS Altair y más tarde TRS-80, Apple II, y otros comenzaron a dominar el mercado de las pequeñas computadoras de propósito general. La última PDP-8 modelos comerciales en 1979 fueron llamados "CMOS-8" y utiliza microprocesadores CMOS personalizados. Ellos no tenían un precio competitivo, y la ofrenda fracasaron. La PC de IBM en 1981 consolidó el destino de la CMOS-8 haciendo un pequeño equipo microprocesador legítima, bien apoyado.

Importancia arquitectónica

La mayor importancia histórica fue que el PDP-8 bajo costo y alto volumen hicieron un ordenador a disposición de mucha gente nueva para muchos usos nuevos. Su importancia es continuar como un ejemplo histórico de diseño por ordenador de valor de ingeniería. Con el tiempo, la mayor parte de la programación en lenguaje de máquina llegó a ser generado por los compiladores y generadores de informes. El ordenador de conjunto de instrucciones reducido regresado de círculo completo a la de PDP-8 énfasis en un simple conjunto de instrucciones y el logro de múltiples acciones en un solo ciclo de instrucción, con el fin de maximizar la velocidad de ejecución, a pesar de los equipos más nuevos tenían palabras de instrucción mucho más largos.

Descripción

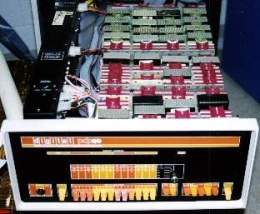

El PDP-8 utiliza las ideas de varios predecesores de 12 bits, en particular la LINC diseñado por WA Clark y CE Molnar que fueron inspirados por el CDC 160 minicomputadora de Seymour Cray. La arquitectura tenía un bus sencillo de E/S programada, además de un canal DMA. El bus de E/S programada se suelen agotarse a los periféricos de velocidad media, tales como impresoras, teletipos, los sacadores de cinta de papel y lectores, mientras DMA se utiliza para pantallas de tubo de rayos catódicos con un lápiz óptico, convertidores de analógico a digital, digital a analógico transformadores, unidades de cinta, unidades de disco. El tamaño de la palabra, 12 bits, es lo suficientemente grande como para manejar enteros sin signo 0-4095 - lo suficientemente amplia como para el control de maquinaria simple. Esto también es suficiente para manejar números con signo -2048 hasta 2047 - Se trata de una mayor precisión que una regla de cálculo o la mayoría de las computadoras analógicas. Doce bits también podrían almacenar dos caracteres ASCII subconjunto de seis bits. Para ahorrar dinero, el diseño utiliza la memoria principal de bajo costo para muchos propósitos, que son atendidas por más caros registros flip-flop en otros ordenadores. Configuración básica del PDP-8 tenía una memoria principal de 4.096 palabras de doce bits. En sus inicios, vista del programador del PDP-8 tenía sólo ocho instrucciones y dos registros. La máquina utiliza memoria de núcleo magnético con un tiempo de ciclo de 1,5 microsegundos, de modo que una instrucción de referencia a memoria de dos ciclos típica corrió a una velocidad de 0.333 MIPS. El PDP-8 se ha optimizado para la simplicidad de diseño. La CPU del modelo de serie, el PDP-8/S, tenía sólo aproximadamente 519 puertas lógicas, mientras que los pequeños microcontroladores generalmente tienen 15.000 o más. Un PDP-8 básico CPU tiene sólo cuatro registros de 12 bits, el acumulador, contador de programa, registro de memoria-tampón y el registro de dirección de memoria. A pesar de su simplicidad básica, el uso de módulos muy pequeños hizo una máquina costosa, con una gran parte del costo hundido en los pequeños módulos, los miles de conectores enchapados en oro, y el complejo de backplane de alambre forrado. En los 8/S dos tensiones lógicas diferentes se utilizaron, una forma económica de aumentar el abanico de salida de la lógica del diodo-transistor barato.

Las versiones de la PDP-8

La cifra total de ventas de la familia PDP-8 se ha estimado en más de 300.000 máquinas. Los siguientes modelos fueron fabricados:

- PDP-8

- LINC-8

- PDP-8/S

- PDP-8/I

- PDP-8/L

- PDP-12

- PDP-8/E

- PDP-8/F

- PDP-8/M

- PDP-8/A

- Intersil 6100 solo chip microprocesador compatible 8-PDP

- Harris 6120 CMOS de un solo chip microprocesador compatible 8-PDP

Entrada/Salida

El sistema de E/S se sometieron a grandes cambios en el PDP-8 era. PDP-8 utilizaba una interfaz de panel frontal, un lector de cinta de papel y una impresora teletipo con una perforadora de papel, cinta opcional. Con el tiempo se añadieron sistemas como la cinta magnética, RS-232 y el bucle de corriente terminales no inteligentes, lectores de tarjetas perforadas, y los discos fijos. Hacia el final de la era del PDP-8, disquetes y unidades de disco de cartucho de cabeza móvil eran populares dispositivos de E/S. Entusiastas modernos han creado adaptadores de disco estándar de PC estilo duro IDE para PDP-8 reales y simuladas.

Instalaciones de programación

Early PDP-8 Sistemas no tienen un Sistema Operativo, un panel frontal y correr y detener switches. Los sistemas de desarrollo de software para la serie PDP-8 comenzó con la entrada del panel frontal más básico de código máquina binario. En la era de la media, se desarrollaron diversas cinta "sistemas operativos" de papel. Muchos programas de utilidades llegaron a estar disponibles en la cinta de papel. 8 PAL-ensamblado de código fuente del lenguaje se almacenaba a menudo en la cinta de papel, leia en la memoria, y se guardaba en la cinta de papel. Hacia el final de la era del PDP-8, sistemas operativos como OS/8 y COS-310 permitian un editor de modo de línea tradicional y el sistema de desarrollo de compiladores de línea de comandos utilizando lenguajes como PAL-III lenguaje ensamblador, FORTRAN, BASIC y DIBOL. Un sistema de tiempo compartido, SAT-8, también estaba disponible. SAT-8 permitia que varios usuarios inicien sesión en el sistema a través de terminales de 110 baudios, y editar, compilar y depurar programas. Incluia una versión especial de BASIC, FORTRAN un subconjunto similar al FORTRAN-1, un subconjunto ALGOL, FOCAL, y un ensamblador llamado PAL-D. Una buena cantidad de software de uso donado para el PDP-8 estaba disponible desde DECUS, la Digital Equipment Corporación Sociedad de usuario y, a menudo venia con listados completos de código y documentación.

Conjunto de instrucciones

Los tres bits de orden superior de la palabra de instrucción de 12 bits son el código de operación. Para los seis operaciones que se refieren a la memoria, los bits 5 a 11 proporcionaban una dirección de 7 bits. Bit 4, si se establece, dice para completar la dirección con los 5 bits de orden superior de la PC, y si claro, se utilizan ceros. Bit 3 especifica indirecto, si se establece, la dirección obtenida como se describe puntos hasta el momento a un valor de 12 bits en la memoria que da la dirección efectiva real de la instrucción.

Páginas de memoria

Este uso de la palabra de instrucción divide las 4096 palabras de memoria en páginas de 128 palabras, el bit 4 de la instrucción seleccionaba la página actual o la página 0. Memoria en la página 0 es un bien escaso, ya que las variables colocadas aquí, se diríjan directamente desde su navegador. El ensamblador estándar colocaba valores constantes para la aritmética de la página actual. Del mismo modo, los saltos entre páginas y llamadas a subrutinas utilizaban una dirección indirecta en la página actual. Fue importante escribir rutinas para caber dentro de las páginas de 128 palabras, o para organizar las rutinas para minimizar las transiciones de página, como referencias y saltos fuera de la página actual requieria una palabra de más.

Las instrucciones básicas

- 000 - Operador de memoria con AC.

- 001 - TAD - Complemento dos, agreguaba el operando de memoria de.

- 010 - ISZ - Incremento del operando memoria y Skip siguiente instrucción si el resultado es cero.

- 011 - DCA - Depósito de CA en el operando de la memoria y Borrar AC.

- 100 - JMS - Saltar a subrutina.

- 101 - JMP - Salto.

- 110 - IOT - Entrada/transferencia de salida.

- 111 - OPR - OPERACIONES microcodificado.

Dispositivo

Bits 3 a 8 de una instrucción IOT seleccionado un dispositivo de E/S. Algunas de estas direcciones de los dispositivos se estandarizaron por convención:

- 00 fue manejado por el procesador y no se envía a un dispositivo de E/S

- 01 por lo general era el lector de cinta de papel de alta velocidad

- 02 fue el golpe de cinta de papel de alta velocidad

- 03 fue el teclado de la consola

- 04 era la impresora consola

Función

Los bits 9 a 11 de una instrucción IOT seleccionaban la función del dispositivo funcional. Los dispositivos simples usarían los bits de forma estándar:

- Bit 11: Provocó que el procesador saltara a la siguiente instrucción si el dispositivo de E/S estaba listo

- Bit 10: Despejado AC

- Bit 9: Movió una palabra entre CA y el dispositivo, inició otra transferencia de E/S, y se aclaró la bandera de "listo" del dispositivo

Estas operaciones se llevaron a cabo en un orden bien definido que dio resultados útiles si se establecian más de un bit.

Control de la memoria

Una palabra de 12 bits puede tener 4.096 valores diferentes, y este fue el número máximo de palabras que el PDP-8 original podría abordar indirectamente a través de un puntero de palabra. Dado que los programas se volvieron más complejos y el precio de la memoria cayeron, se hizo deseable ampliar este límite. Para mantener la compatibilidad con los programas ya existentes, un nuevo hardware fuera del diseño original añade bits de orden superior a las direcciones efectivas generados por el programa. El controlador de extensión de memoria ampliado la memoria direccionable por un factor de 8, hasta un total de 32.768 palabras. El esquema de memoria extendida dejó programas existentes manejar el aumento de memoria con cambios mínimos. Por ejemplo, 4K FOCAL normalmente tenía unos 3K de código con sólo 1K de sobra para programa de usuario y datos. Con unos pocos parches, FOCAL podría utilizar un segundo campo de 4K para el programa de usuario y datos. Por otra parte, los campos de 4K adicionales podrían ser asignados a los usuarios separados, girando 4K FOCAL en un sistema de tiempo compartido multi-usuario.

Virtualización

En los modelos PDP-8/E y más tarde, el controlador de extensión de memoria se ha mejorado para permitir la virtualización de la máquina. Un programa escrito para usar un PDP-8 recursos de enteros podía coexistir con otros programas en el mismo PDP-8 bajo el control de un gestor de máquina virtual. El gerente podría hacer todas las instrucciones IO causan una trampa. De esta manera, el administrador podría asignar referencias de memoria, los datos del mapa o campos de instrucción, y redirigir IO a diferentes dispositivos. Cada programa original tuvo acceso completo a una "máquina virtual" proporcionada por el gerente.

Lista de enlaces

Otra subrutina posible para el PDP-8 era una lista enlazada. GETN, 0/Obtiene el número señalado y se mueve el puntero del CLA CLL/Clear acumulador TAD I PTR/Obtiene el número apuntaban a DCA TEMP/Save valor actual ISZ PTR/Incremento puntero TAD I PTR/Obtiene la siguiente dirección de DCA PTR/Dejar puntero JMP I GETN/retorno PTR, 0 TEMP, 0

Interrupciones

No había una sola línea de interrupción en el bus de E/S PDP-8. El procesador maneja cualquier interrupción mediante la desactivación de otras interrupciones y ejecutar un JMS a la ubicación 0000. Como era difícil escribir subrutinas reentrantes, era difícil interrumpe nido y esto por lo general no se hizo; cada interrupción corrió hasta su finalización e interrumpe re-habilitados justo antes de ejecutar la instrucción JMP I 0 que volvió de la interrupción. Debido a que sólo había una sola línea de interrupción en el bus de E/S, la ocurrencia de una interrupción no informó el procesador de la fuente de la interrupción. En su lugar, la rutina de servicio de interrupción tuvo que sondear en serie cada dispositivo de E/S activa para ver si era la fuente. El código que hizo esto se llama una cadena de salto, ya que consistía en una serie de PDP-8 "prueba y saltar si la bandera establece" instrucciones de E/S. La prioridad de interrupción relativa de los dispositivos de E/S se determinó por su posición en la cadena de salto: Si varios dispositivos interrumpidos, el dispositivo de prueba anterior de la cadena de salto sería atendida primero.